#### **SYNOPSYS**<sup>®</sup>

# Opportunities for HPC in the design and manufacturing of semiconductor systems

Rob Aitken, Distinguished Architect October 18, 2023

# **IMPORTANT NOTICE**

In the event information in this presentation reflects Synopsys' future plans, such plans are as of the date of this presentation and are subject to change. Synopsys is not obligated to update this presentation or develop the products with the features and functionality discussed in this presentation. Additionally, Synopsys' services and products may only be offered and purchased pursuant to an authorized quote and purchase order or a mutually agreed upon written contract with Synopsys.

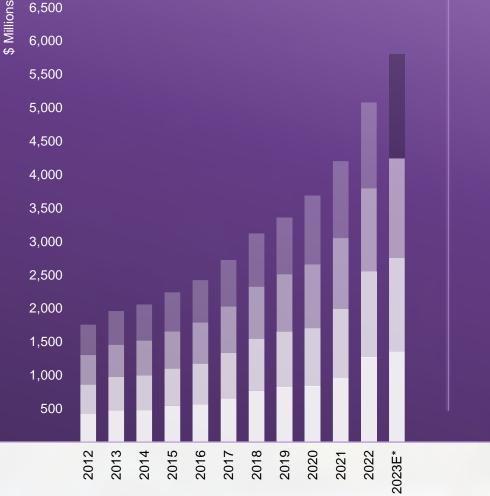

#### Synopsys overview

6,500

\$5.8B Revenue (TTM)

19,985+ Employees

3,322 Patents

118 Offices **#1** Electronic design automation tools and services

**Broadest IP portfolio**

and #1 interface, foundation and physical IP

Leader in Gartner's Magic Quadrant for application security testing

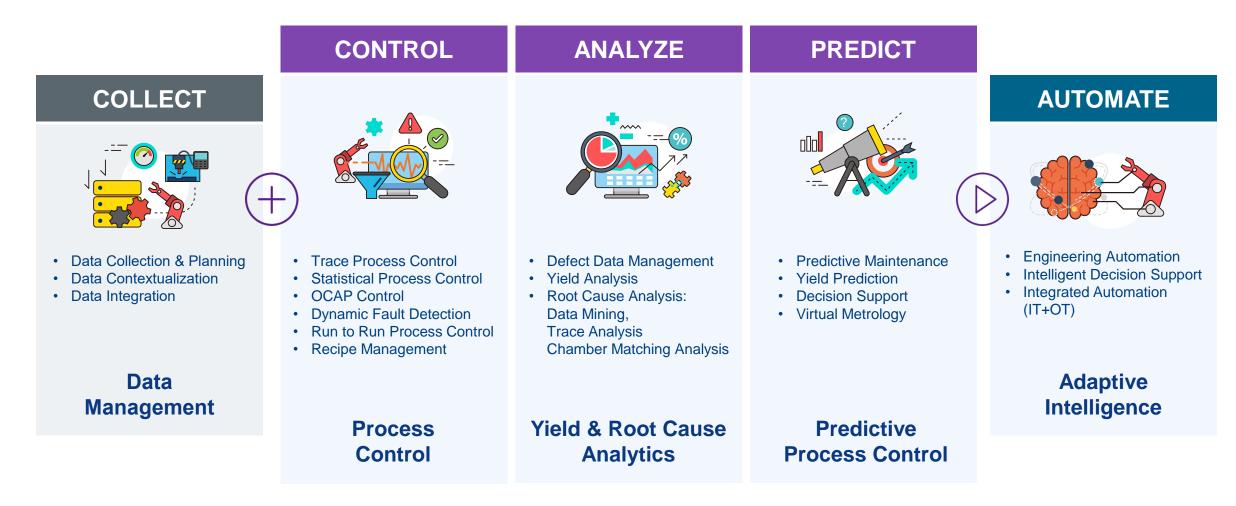

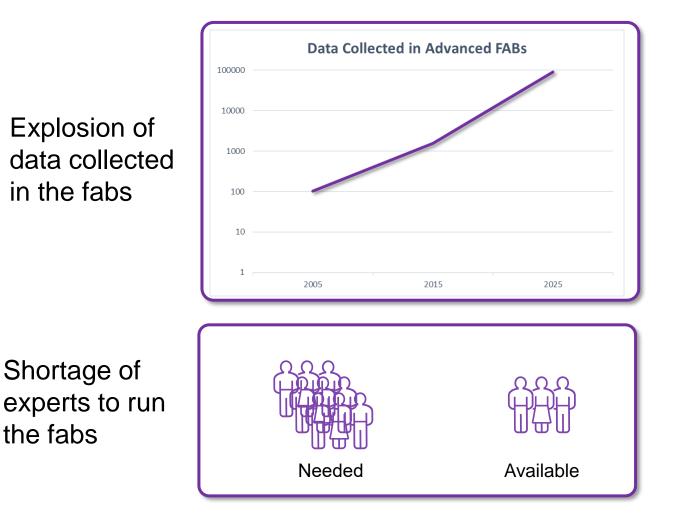

#### Towards "Lights Out" Fabs

**SYNOPSYS**<sup>®</sup>

# Conventional Process Control Solutions Struggling to Meet Industry Needs

- Solutions are not scaling with the needs of giga fabs

- Petabytes of data, thousands of manufacturing "tools"

- Analysis time for root cause takes longer

- Late or inaccurate decisions increase scrap and production cost

- Industry needs a new paradigm for process control

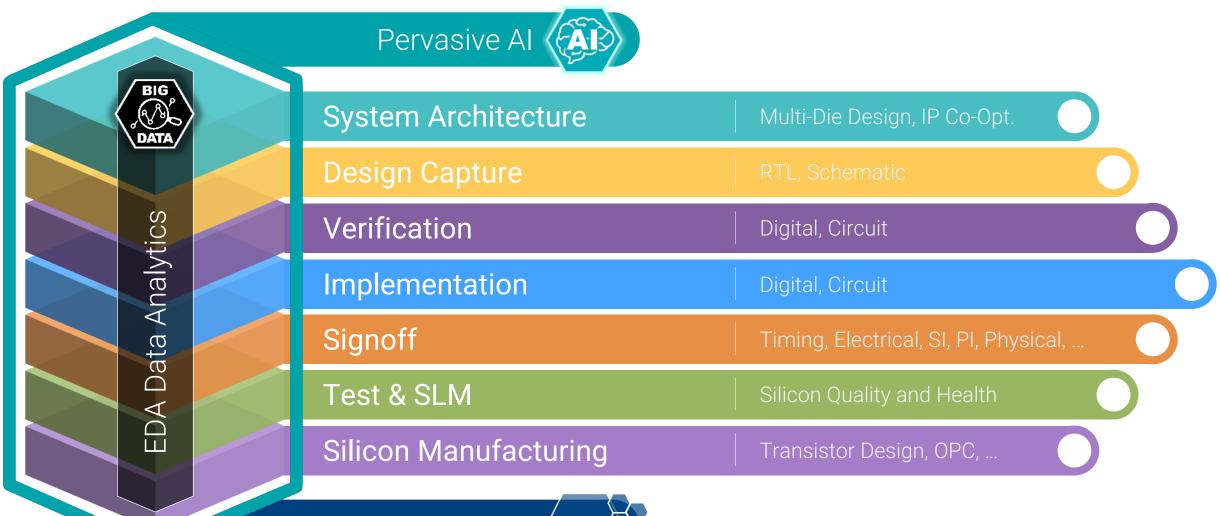

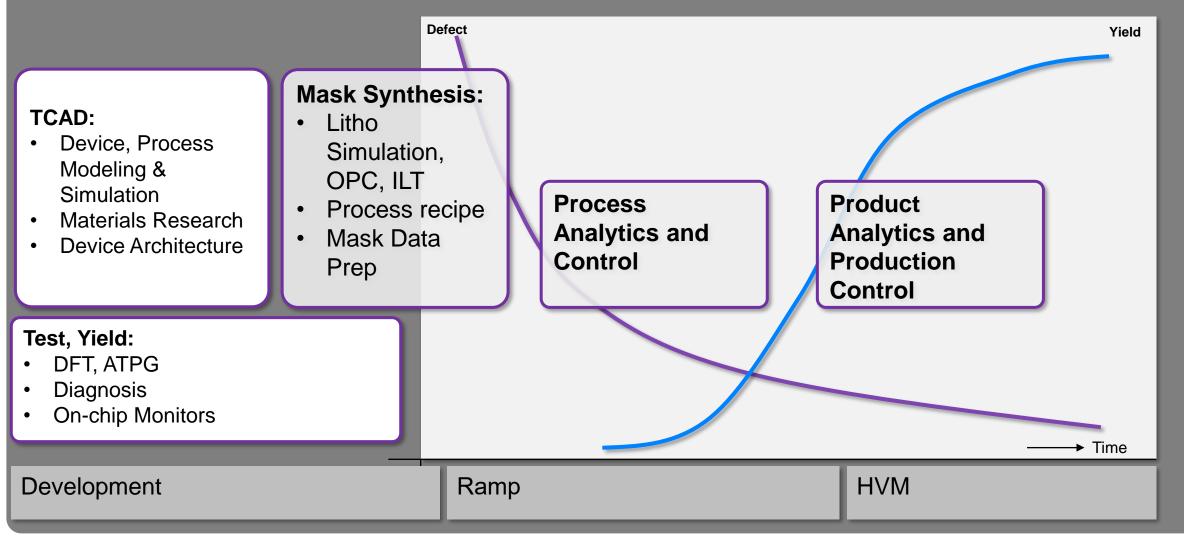

#### Electronic design automation flow

Hyperconvergence

## Software-centric view of IC Manufacturing

Simplified flow

**SYNOPSYS**°

## EDA algorithms at a glance

- Graph traversal, matrix solvers, compilers, database manipulation, ...

- NP Hard, 40+ years of heuristics

- Most originally developed with a single workstation, NFS worldview

- Genetic algorithms, neural networks, deep learning etc. added/tried since the 1990s

- Massive scale

- Millions to billions of instances, limited by compute capacity not problem size

- Partitioning designs is a major implementation challenge

- Wide range of inherent parallelization possibilities

- From straightforward to "nobody knows how"

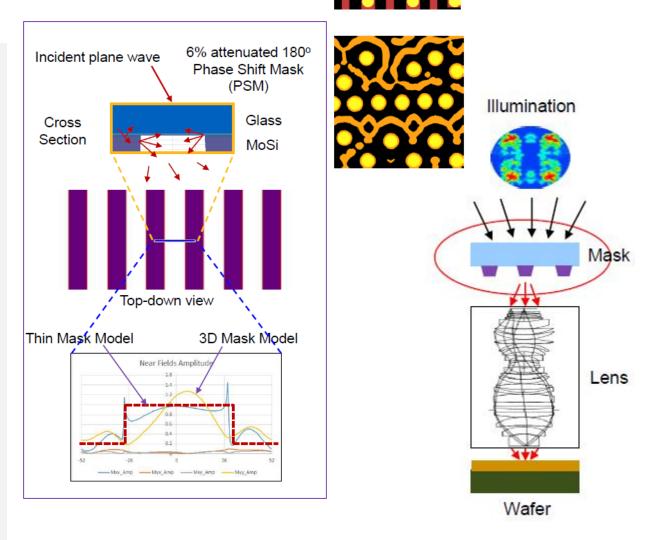

# Example: mask making for lithography

When what you see isn't what you get

- Hundreds of billions of features on a modern chip

- Optical lithography uses 193nm light to print much smaller features

- Designing masks (Inverse Lithography Technology, ILT) requires complex 3D manipulation of light, in theory solving Maxwell's equations

- Highly parallelizable

- Originally CPU based

- Algorithms can be restructured to be more GPU friendly

- Further optimization possible for customized accelerators

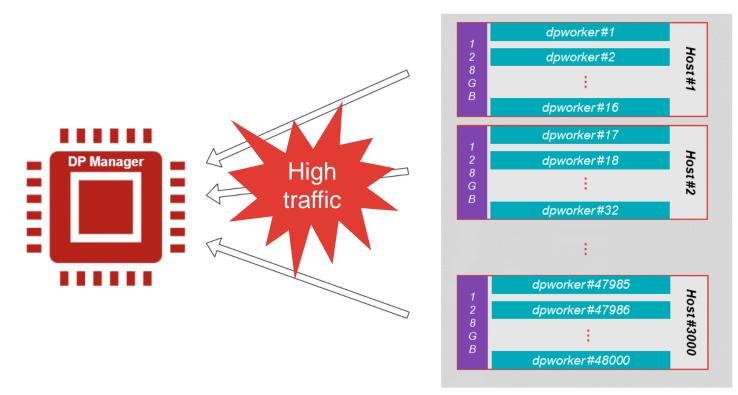

#### Expanding to datacenter scale

- Full chip (100B+ features) ILT can easily use 100k workers

- 24-hour turnaround desired

- After algorithm parallelization complete, Posix file system and communication to manager task biggest bottlenecks to scaling

- Intercept file system API to reduce communication and enable scaling to multiple datacenters

# Summary and future opportunities

- 40+ years of optimization in Electronic Design Automation

- Moore's law kept a balance between problem complexity and solution capability

- Data and complexity explosion in semiconductor manufacturing

- Datacenter scale and AI/ML offer promise for HPC solutions